教程演示🔗

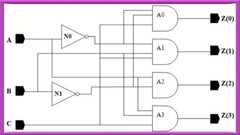

基于FPGA的设计

你将学到什么

-

数字电路的 Verilog 编码

要求

-

不

描述

完成本课程后,学员将能够:

(1) 了解设计工程师要优化的概念设计指标

(2)了解IC设计技术的概念

(3)了解使用固定功能IC技术、全定制ASIC技术和半定制ASIC技术的逻辑实现

(4) 了解使用固定功能IC技术、全定制ASIC技术和半定制ASIC技术实现逻辑的优缺点

(5)理解PLD中逻辑实现的概念

(6)理解FPGA中逻辑实现的概念

(7)了解IC设计流程

(8)理解HDL在系统设计中的作用

(9) 理解各种Verilog语言结构的概念

(10)了解各种运算符及其在Verilog编码中的用途

(11)了解如何使用Xilinx软件编写Verilog代码

(12)了解如何使用Xilinx软件模拟Verilog代码

(13)了解如何使用Xilinx软件实现Verilog代码

(14)使用行为建模风格实现组合逻辑

(15) 使用数据流建模风格实现组合逻辑

(16) 使用结构建模风格实现组合逻辑

(17) 使用行为建模风格实现顺序逻辑

(18) 使用数据流建模风格实现顺序逻辑

(19) 使用结构建模风格实现时序逻辑

(20)利用mos管实现逻辑

本课程适合谁:

- 有兴趣编写和模拟为组合电路和时序电路编写的 verilog 代码的学生

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。