PCIe Gen 6.0 协议:从基础到高级(VLSI)

掌握 PCIe Gen 6:让您对每一层都有独到的见解

学习内容:

* PCIe Gen6 的主要特性和进步。

* 如何使用高速通道传输数据。

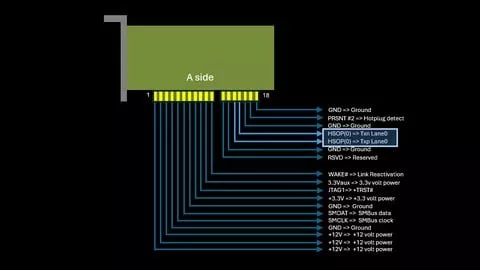

* PCIe 架构的物理层和协议层。

* 错误管理、电源效率和安全机制。

* 实际应用和系统设计考虑。

课程内容主题:

* 硬件

* 信息技术与软件

课程要求:

* 对计算机架构和 I/O 接口的基本了解。

* 了解数字电子学和数据通信原理。

* 可选择具有硬件设计或嵌入式系统经验。

* 对高速接口和系统集成感兴趣。

课程详细描述:

本课程专为设计和 ASIC 验证工程师量身定制,深入解析 PCIe Gen 6 技术的核心内容。PCIe(外围组件互连快速)作为现代高速互连系统的基石,Gen 6 在带宽、效率和兼容性方面实现了重大突破,满足下一代计算、网络和存储应用的需求。课程全面覆盖 PCIe Gen 6 的事务层架构,重点讲解地址空间管理、事务路由以及与前代产品的差异化增强功能。

通过结构化模块,学员将掌握以下关键知识:

– **数据包格式与流控制机制**:包括 FLIT(流控制单元)编码的引入,这是实现 Gen 6 高带宽能力的核心技术。

– **向后兼容性**:深入探讨 PCIe Gen 6 与早期版本的兼容性,确保无缝集成到现有系统中。

– **性能提升**:解析 Gen 6 如何实现 Gen 5 带宽的两倍提升,同时优化电源效率和系统可扩展性。

– **高级技术挑战**:涵盖高速信号处理、PAM4 编码、时钟要求及 Gen 6 独有的错误处理机制。

– **设计与验证策略**:结合行业标准方法(如 UVM 通用验证方法),提供实用设计考虑和验证案例,包括真实场景分析与合规性测试。

课程适合以下人群:

– 想要学习 PCIe 协议的初学者。

– 希望提升知识水平的职场人士。

– 正在设计 PCIe 协议的 VLSI 设计工程师。

– 需要验证 PCIe 协议场景的 VLSI 验证工程师。

通过本课程,学员将具备设计和验证 PCIe Gen 6 系统的专业能力,为高性能计算和数据密集型应用的开发提供坚实基础。