数字IC/FPGA设计P3:常用硬件架构

向复杂IP设计迈出一大步

学习内容:

SRAM的行为和使用建议

握手接口和同步FIFO

流水线至最大时钟频率

仲裁者设计

跨时钟域(CDC)和异步FIFO

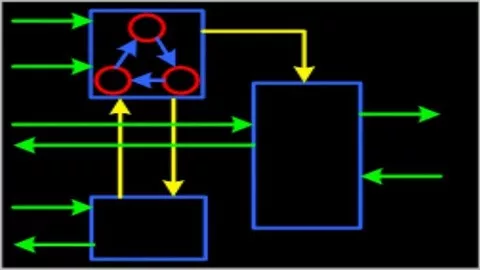

乒乓架构

带控制(反馈)的流水线

具有危险和前向路径的流水线

滑动窗口架构

课程内容主题:

SRAM行为与应用

握手接口与同步FIFO设计

流水线优化与时钟频率提升

仲裁器设计(包括轮询与非仲裁方案)

跨时钟域(CDC)与异步FIFO实现

乒乓架构与矩阵转换实践

带控制信号的流水线设计

流水线冒险与前向路径处理

滑动窗口算法与二维高斯滤波设计

2D DMA控制器项目(APB+AXI接口)

课程要求:

掌握数字电路基础理论

具备C/C++编程语言基础

熟悉Verilog硬件描述语言

课程详细描述:

本课程系统讲解数字IC/FPGA设计中常用的硬件架构,涵盖SRAM、同步FIFO、流水线、仲裁器、跨时钟域处理、乒乓架构、滑动窗口等核心内容。课程通过理论讲解与实战编码结合的方式,帮助学员掌握复杂IP设计的关键技术。

课程包含12+编码练习与3个完整项目,包括:

– SHA-256算法实现(简单接口与APB/AXI接口版本)

– 基于APB/AXI接口的2D DMA控制器设计

每个硬件架构章节后均附带编码练习与参考代码,难度从数行代码逐步提升至千行级项目,最终项目规模超过1000行。

课程内容覆盖数字IC设计全流程,包括:

理论部分:MOS晶体管→逻辑单元→算术数据路径→Verilog语言→硬件功能模块→时序分析(STA)→片上总线(APB/AHB-Lite/AXI4)→低功耗设计→可测性设计(DFT)→系统级芯片(SOC)

实践部分:FSM、流水线、仲裁器、CDC、同步/异步FIFO、乒乓架构、滑动窗口、收缩阵列等核心模块设计

适合对象:

– 电气工程专业高年级本科生及以上

– 具备0~2年经验的IC设计/验证工程师

通过本课程,学员将掌握RISC-V CPU核心、AI加速器等复杂系统设计所需的架构知识,为进入VLSI/FPGA领域奠定坚实基础。