VHDL for an FPGA Engineer with Vivado Design Suite

使用Xilinx FPGA的VHDL开发实战

学习内容:

* 掌握VHDL编程基础,提升RTL工程师职位面试竞争力

* 理解Vivado Design Suite数字系统设计流程

* 学习如何编写可综合的RTL代码

* 掌握硬件描述语言中的多种建模风格及VHDL并发/顺序语句

* 学习使用Xilinx IP核及创建自定义IP的方法

* 熟悉Vivado IP Integrator设计流程

* 编写VHDL测试平台(Testbench)

* 掌握Vivado硬件调试技术(集成逻辑分析仪、虚拟I/O)

* 从零基础到精通VHDL开发全流程

课程内容主题:

* Vivado安装与许可证配置

* FPGA性能对比与开发动机

* Vivado设计流程详解(含RTL分析、综合、实现等阶段)

* 信号与变量基础

* 数据流建模风格(含算术运算、移位操作、多比特向量处理等)

* 行为建模风格(含进程块、条件语句、状态机设计等)

* 测试平台编写与验证方法

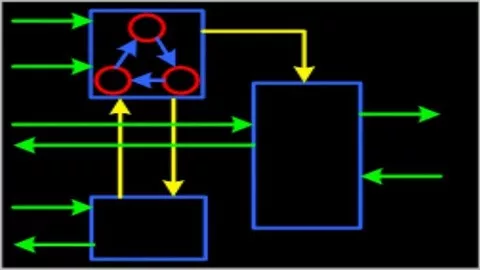

* 结构化建模风格(含模块化设计、IP核集成等)

* FPGA硬件调试与优化策略

课程要求:

* 具备数字电路基础理论知识(如逻辑门、时序分析等)

* 熟悉基本计算机操作及EDA工具使用逻辑

* 无需编程经验,课程从零基础开始教学

课程详细描述:

* 本课程聚焦VHDL语言,结合Xilinx Vivado Design Suite工具链,系统讲解FPGA开发全流程。

* 通过大量实例解析数据流、行为级、结构化建模等不同风格,帮助学员掌握RTL设计核心技巧。

* 深入讲解Vivado综合、实现、调试等关键阶段,包含IP核集成、硬件调试(ILA/VIO)等高级功能。

* 覆盖从基础语法到复杂系统设计的完整知识体系,包含计数器、状态机、总线接口等典型模块实现。

* 适合VLSI求职者、ASIC/VLSI领域新人及希望掌握FPGA开发技术的工程师,助力职业发展。

* 课程包含19.5小时高清视频、39篇技术文档及多个实战项目,提供永久学习权限与结业证书。