数字定时基础:VLSI面试与SoC设计

掌握静态时序分析(STA)与数字逻辑设计的核心概念

学习内容:

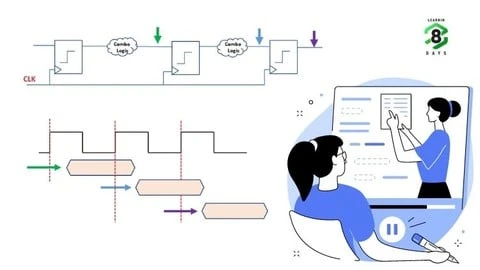

* 触发器和锁存器时序基础知识

* 建立时间、保持时间、时钟至Q延迟与时钟偏移

* 建立和保持违规检查与修复方法

* 延迟最小化策略与实现

* 数字电路中的建立和保持裕度分析

* 最小与最大路径分析技术

* 时钟门控设计原理

* SoC中的频率-电压(F-V)曲线分析

课程内容主题:

* 引言:VLSI设计与时序分析的重要性

* 触发器时序基础:定义、建立时间、保持时间、时钟至Q延迟

* 静态时序分析基础:缓冲器、逻辑实现、物理实现、周期路径分析

* 面试问题解析:建立与保持裕度计算、违规修复、延迟优化

* 高级概念:正负锁存器时序、时钟门控、负建立/保持时间

* 常见误区:时钟偏移、频率对裕度的影响

* SoC设计中的频率与电压关系(F-V曲线)

* 实际设计问题分析:多路径优化、操作频率限制

课程要求:

* 具备基本的触发器功能知识

* 熟悉数字逻辑设计基础概念

* 对VLSI设计流程有初步了解

课程详细描述:

* **核心内容**:全面覆盖触发器、锁存器及逻辑门的时序特性,包括建立时间、保持时间、时钟至Q延迟等关键指标,结合静态时序分析(STA)方法,深入解析建立与保持裕度的计算及优化策略。

* **实战应用**:通过真实案例分析建立与保持违规问题的修复方法,学习如何通过设计优化降低延迟,提升电路性能。

* **高级主题**:探讨正负锁存器的时序特性、时钟门控技术,以及SoC设计中频率与电压(F-V曲线)的平衡策略。

* **面试准备**:针对VLSI面试高频问题,提供系统化解决方案,涵盖多路径分析、操作频率限制等实际设计挑战。

* **讲师背景**:由VLSI行业专家授课,内容融合德州仪器、AMD、英特尔等企业实战经验,确保理论与实践深度结合。

* **适用人群**:VLSI学生、物理设计工程师、RTL设计师、验证工程师、SoC设计师及半导体行业从业者,助力职业发展与面试准备。