验证与系统Verilog基础

面向学生和工程师的验证概念与SystemVerilog基础课程

学习内容:

* 理解验证的意义与重要性

* 掌握验证方法、技术选项及实施计划

* 在EDA Playground等工具上实践验证案例

* 学习测试平台(Testbench)的核心原理

* 编写SystemVerilog代码并掌握其语法

* 熟悉SystemVerilog中的数据类型(包括用户自定义类型)

* 掌握过程语句(Procedural Statements)的使用

* 理解接口(Interface)的设计与实现

课程内容主题:

* 课程介绍与典型VLSI设计流程

* 验证方法论与技术挑战

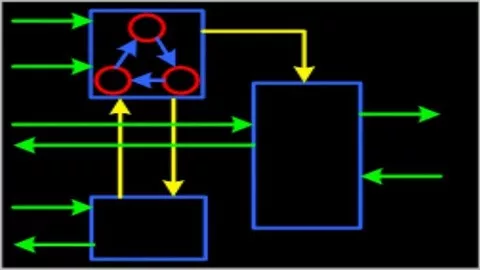

* 测试平台分层结构与功能

* SystemVerilog数据类型详解(数组、队列、关联数组等)

* 用户自定义数据类型与包(Package)设计

* 过程控制语句(函数、任务、阻塞/非阻塞赋值)

* 接口设计与跨模块通信实现

* 验证计划制定与常见面试问题解析

课程要求:

* 具备Verilog编程基础及FPGA开发知识

* 熟悉C/C++语言者优先

* 了解数字电路设计原理

课程详细描述:

本课程为希望掌握验证基础概念及SystemVerilog核心知识的学习者设计,适合电子工程学生、验证工程师及求职者。课程从验证的必要性入手,系统讲解验证方法论、测试平台构建、SystemVerilog数据类型与接口设计等关键内容。通过大量实例与EDA Playground实践,帮助学员掌握从基础语法到复杂验证场景的完整技能链。课程包含分层测试平台设计、动态数组与队列操作、接口通信实现等进阶主题,并通过章节测验与练习巩固学习成果。讲师结合24年教学经验,以清晰的逻辑与实战案例,助力学员快速掌握验证领域核心技能,应对行业实际需求。

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。