VLSI/FPGA设计P2:Verilog用于设计和验证

通过示例学习,实现电路图、RTL代码和波形的一致性

学习内容:

* 掌握设计和验证常用的Verilog语法

* 学习在Windows系统上安装Verilator和GTKwave(使用WSL)

* 描述组合逻辑(基本逻辑门、多路复用器、解码器、独热解码器)

* 描述顺序逻辑(同步/异步复位DFF、计数器、边缘检测、移位寄存器、序列检查、sync_fifo)

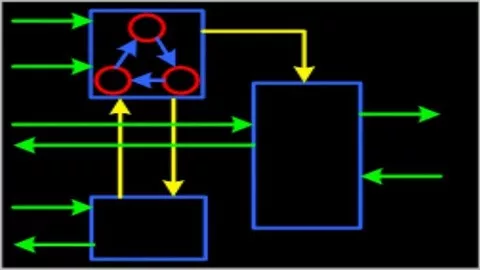

* 设计有限状态机(FSM)

* 编写测试平台

* 使用Verilator和GTKwave调试设计

* 了解综合常见错误(不完整的敏感列表、锁存器、多驱动、组合逻辑循环)

* 练习时间:设计与验证z-scan功能、复杂序列检查(FSM)

课程内容主题:

* Verilog HDL编程

* 硬件

* IT与软件

课程要求:

* 具备基础C或C++编程语言知识

* 掌握数字电路基础知识

课程详细描述:

* 课程通过示例和编码练习,帮助学员在不到10小时的视频学习中掌握电路图、Verilog代码和波形之间的一致性。

* 内容涵盖数字IP/IC设计流程、Verilog常用语法、组合逻辑与顺序逻辑设计、有限状态机(FSM)构建、测试平台编写及常见综合错误分析。

* 课程包含多个实践项目,如z-scan功能设计、复杂序列检查(FSM)等,逐步提升学员的编码能力。

* 课程内容分为11个章节,包括安装工具、语法讲解、电路设计、调试技巧及高级主题,适合初学者到进阶学习者。

* 课程由资深工程师讲师授课,结合理论与实践,帮助学员掌握VLSI/FPGA设计的核心技能,为进入该领域奠定基础。

* 课程适合任何希望学习Verilog和数字IC/FPGA设计的学习者,无论是否具备相关经验。

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。