教程演示🔗

你会学到什么

-

学习 Verilog HDL 编程的基本概念和属性与 C 语言的比较,Verilog HDL 相对于 VHDL 的特性和优势

-

VLSI 设计流程(FPGA 和 ASIC)以及 FPGA 与 ASIC 之间的区别

-

Verilog HDL 编程中的不同设计方法及示例

-

具有阻塞和非阻塞概念的行为建模以及实时示例

-

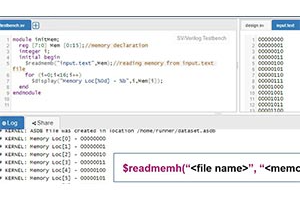

带有示例的测试平台 Verilog 程序

-

任务和系统任务,包括随机数据生成器、基于文件的操作和内存加载操作以及文件表示输入和输出等示例。

-

有限状态机 (FSM) 以及 Mealy & Moore 和序列检测器 FSM 的示例

-

内存控制器的完整设计和测试平台编程

-

FIFO 控制器的完整设计和测试台编程

-

用于汉明码错误检测校正的编码器和解码器的完整设计和测试台编程

-

FPGA基础知识

要求

-

学习意向

-

C语言基础

-

数字设计基础知识(非强制性)

描述

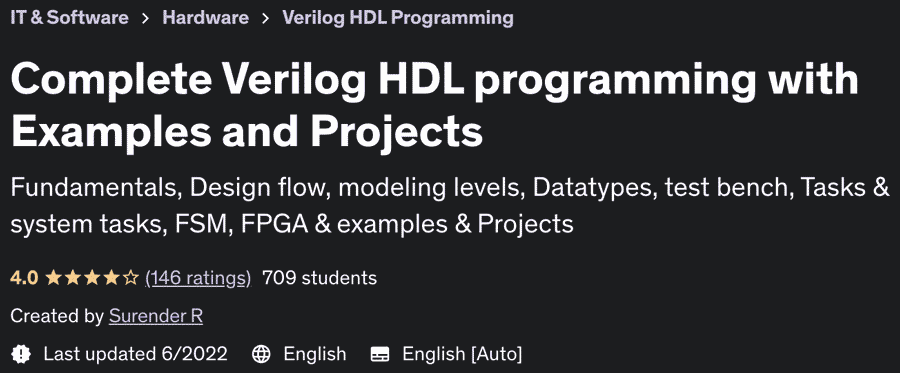

完整的 Verilog HDL 编程课程,从基础水平到应用水平,为初学者和有经验的人提供完美、结构良好和简洁的课程。本课程讨论 Verilog HDL 编程中的概念和与 C 语言相比的属性,并讨论其特性和优势。

在本课程中,我们提供与 FPGA 和 ASIC 的 VLSI 设计流程相关的信息,并对两者进行概述。

本课程提供有关不同编程风格的信息,例如门级、数据流、行为和开关级以及示例。

本课程提供了关于验证的清晰画面,即模拟和编写测试台以及一些通用示例,如计数器、使用计数器的时钟驱动器、脉冲发生器。

本课程解释了如何使用带有任务的测试平台和带有示例的系统任务来编写验证模型。这些示例包括基于文件的系统任务,例如将数据写入文件、从文件读取数据以及将数据加载到内存和随机数据生成器。

本课程清晰地展示了有限状态机 (FSM)

如何绘制,

如何在硬件模型中实现

ro 如何通过示例转换为 Mealy & Moore FSM 的 verilog 代码。

本课程还展示了一些项目,如内存控制器、FIFO 控制器和使用汉明码的错误检测和纠正,这提高了分析和处理项目的能力。

最后给出了FPGA类核心概念的基本知识,位文件是如何加载到FPGA中的。

本课程适合谁:

- 本科电子和计算机科学工程专业学生

- 计划从事VLSI领域前端(Design & verification)的研究生

- 高级在读研究生,愿意做前端VLSI设计项目

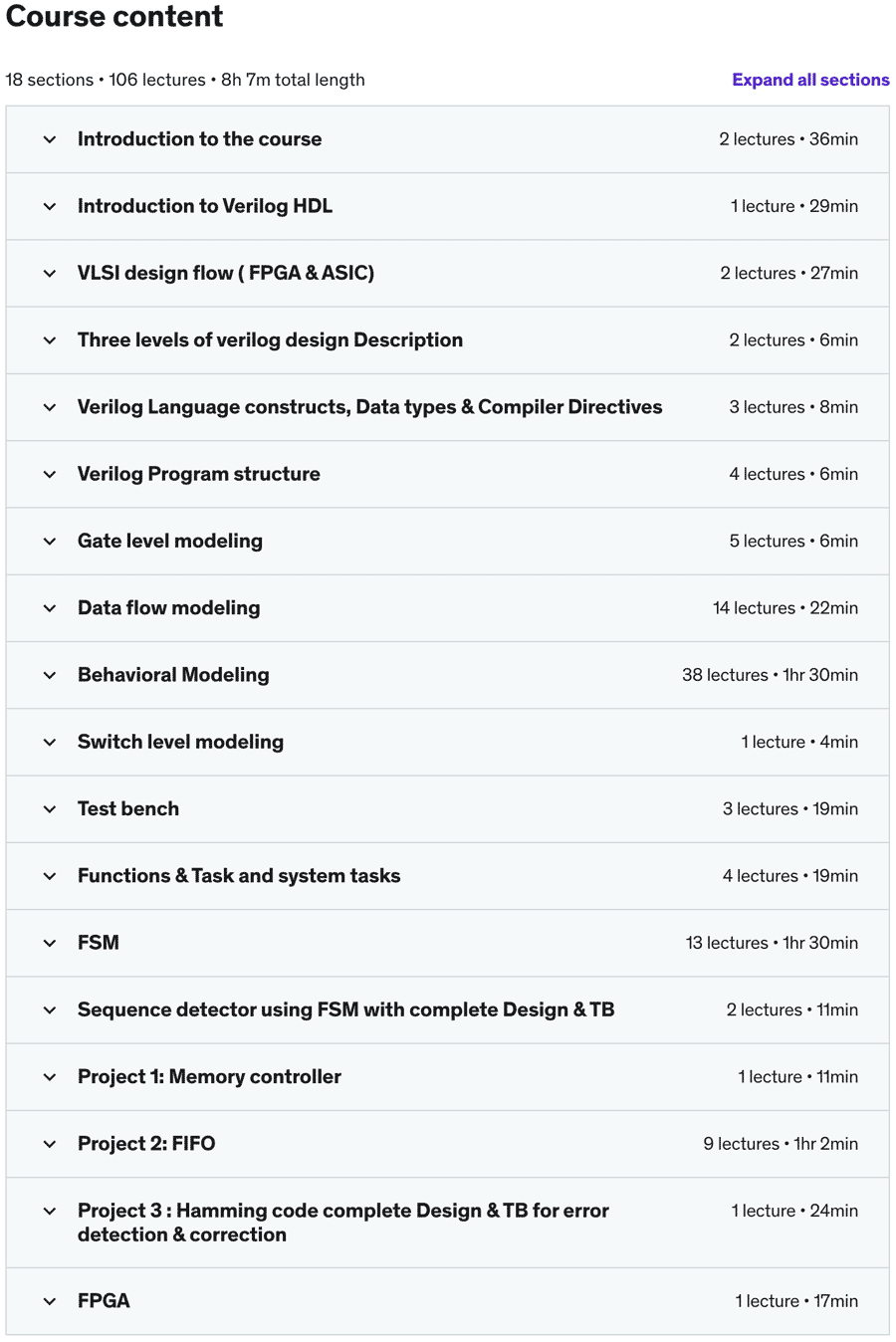

课程主题

图片

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。