教程演示🔗

课程描述

本课程涵盖高级综合 (HLS) 设计流程中的高级主题。本课程的目标是仅使用 C/C++ 语言在 FPGA 上描述、调试和实现逻辑电路,而无需任何 HDL(例如 VHDL 或 Verilog)的帮助。 HLS 最近被一些行业领导者(如 Nvidia 和 Google)用于设计他们的硬件和软件平台。 HLS 设计流程是硬件设计的未来。它很快成为每个热衷于利用 FPGA 的卓越性能和低功耗的硬件或软件工程师的必备技能。本课程率先讲解高级HLS设计流程主题。它使用 Xilinx HLS 软件和硬件平台来演示真实示例和应用。

在整个课程中,您将学习几个描述 HLS 概念和技术的示例。该课程包含大量测验和练习,以练习和掌握所提出的方法和方法。本课程是在目标 FPGA 上设计硬件模块和加速算法的 HLS 系列课程的第三部分。本课程侧重于 HLS 中的多周期设计、高级设计和优化技术,而该系列的其他课程则介绍如何使用单周期设计技术在 HLS 中开发组合和时序逻辑电路。

你会学到什么

- 使用多周期设计流程在 HLS 中开发时序电路。

- 在HLS中实现流通信和计算

- 使用 FIFO 作为连接模块之间的同步机制

- 学习如何在 HLS 代码中使用数组变量

- 在 Vivado 项目中连接和与 HLS IP 到 BRAM

- 在 HLS 中使用指针

- 在 HLS 中使用 AXI 协议

- HLS 中的循环流水线优化

- HLS 中的循环展开优化

- HLS 中的循环扁平化优化

- HLS 中的循环倒带优化

- 在 HLS 中使用 HLS-Stream 库

- HLS 中的握手协议和接口

本课程适合谁

- 硬件工程师

- 对FPGA感兴趣的软件工程师

- 希望在讲座、课程或研究中使用基于 FPGA 的 HLS 的讲师、研究人员和教授

- 数字逻辑爱好者

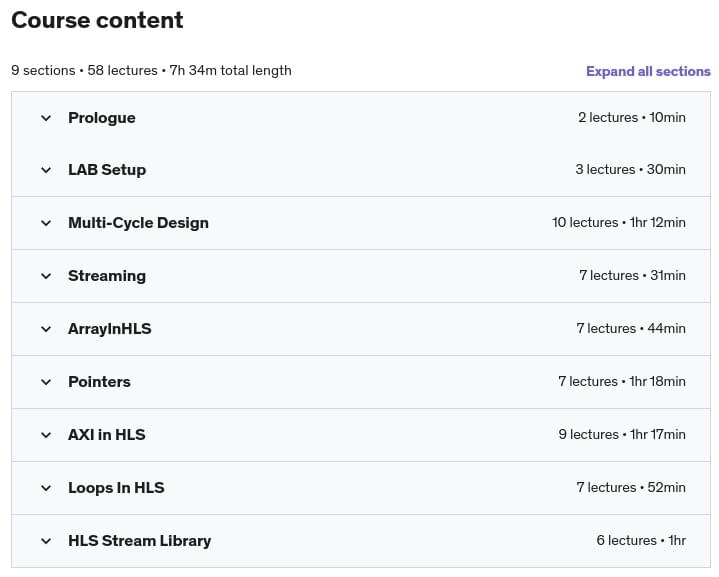

FPGA 高级综合规范,第 3 部分 – 高级

- 发行商:Udemy

- 老师:穆罕默德侯赛因巴迪

- 英语语言

- 级别 : 中级

- 课程数 : 58

- 时长:7小时33分钟

FPGA 高级综合的内容,第 3 部分 – 高级

要求

- 了解 C/C++ 编码的基本概念

- 了解逻辑运算符的基本概念(例如,AND、OR、XOR、SHIFT)

- “FPGA 的高级综合,第 1 部分 – 组合电路”Udemy 课程

- “FPGA 高级综合,第 2 部分 – 时序电路”Udemy 课程

- BASYS3评估板

- Xilinx Vitis-HLS 和 Vivado(下载 Vivado ML 版本或 Vivado Design Suite – 适用于 Windows 或 Linux 的 HLx 版本)

图片

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

![用于 FPGA 接口的 VHDL 格式的 I2C、SPI、UART (RS232)、VGA[I2C, SPI, UART (RS232), VGA in VHDL for FPGA interfacing]](https://www.postcode.vip/wp-content/uploads/2023/07/1688602695-45c48cce2e2d7fb.jpg)