教程演示🔗

你会学到什么

-

Verilog 编程基础知识,有助于在 RTL 工程师工作面试中取得优异成绩。

-

了解用于数字系统设计的 Vivado Design Suite 流程。

-

Vivado 中的硬件调试即。集成逻辑分析仪,虚拟 I/O。

-

硬件描述语言中的不同建模风格。

-

如何使用 Xilinx IP 和创建自定义 IP。

-

IP 集成器 Vivado 的设计流程。

-

编写 Verilog 测试平台。

-

一些现实世界项目的设计,例如:PMOD DA4 DAC 接口、函数发生器、小型处理器架构、UART 接口、PWM、用于开发板的 BIST 等等。

-

常见面试问题

要求

-

数字电路基础将提供额外的优势。

描述

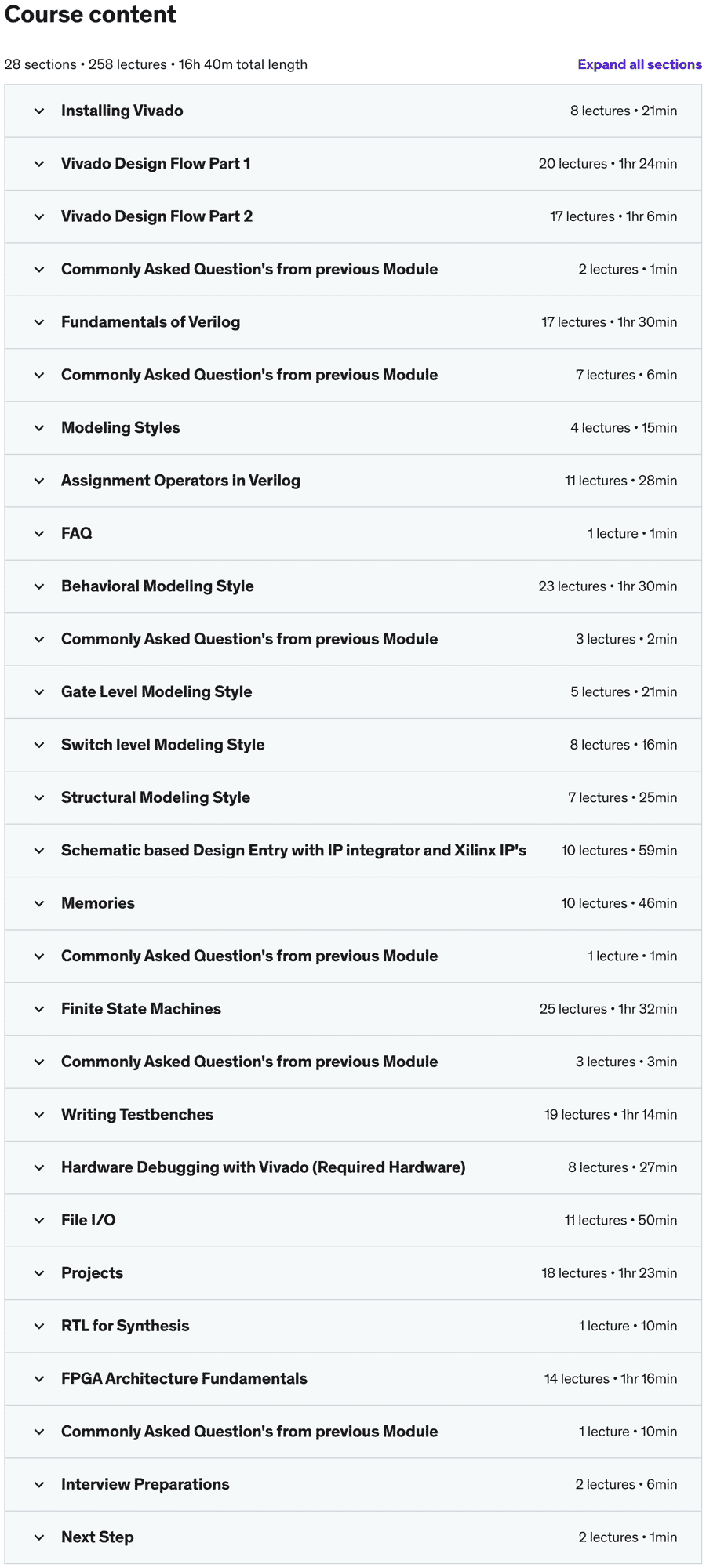

FPGA无处不在,它们在不同领域的存在日益增加。两种最流行的硬件描述语言是 VHDL 和 Verilog,每种语言都有其独特的优势。关于它们两者的最好的部分是,一旦您知道其中一个,您就会自动理解另一个,然后两个世界的功能都可以用于构建复杂的系统。本课程侧重于 Verilog 语言。通过分析在该领域工作的大多数公司所需的最常见技能来制定课程。大多数概念的解释都考虑了实际的例子,以帮助建立逻辑。

该课程说明了建模风格、阻塞和非阻塞分配、可合成 FSM、使用块和分布式内存资源构建内存、Vivado IP 集成器以及 ILA 和 VIO 等硬件调试技术的用法。本课程使用 Xilinx Vivado 设计套件探索 FPGA 设计流程,并讨论实现所需性能的实施策略。详细说明了许多项目,以了解 Verilog 结构的使用,以将实际外围设备连接到 FPGA。关于编写 Testebench 和 FPGA 架构的单独部分进一步加深了对 FPGA 内部资源和执行设计验证步骤的理解。

本课程适合谁:

- 希望从事 RTL 工程师/设计工程师/验证工程师职业的 VLSI 求职者/研究生。

- 任何有兴趣学习 Xilinx FPGA/Vivado Design Suite/Verilog 硬件描述语言的人

- 任何有兴趣在 ASIC/VLSI 领域开始职业生涯的人。

适用于具有 Xilinx Vivado 设计套件先决条件的 FPGA 工程师的 Verilog

数字电路基础将提供额外的优势。

图片

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。