Verilog HDL 通过示例学习

从零开始掌握数字电路建模

学习内容:

* Verilog 硬件描述语言

* Verilog HDL 中的数字设计

* 使用 Verilog HDL 建模数字电路

* 数字电子学基础

课程内容主题:

* Verilog HDL 编程

* 硬件

* 信息技术与软件

课程要求:

* 具备数字电子学的基础知识

课程详细描述:

* **课程亮点**:

– 清晰区分编程语言(如 C、C++、Python)与硬件描述语言(如 Verilog、VHDL、SystemVerilog)的核心差异。

– 通过标准组合逻辑电路和时序电路,深入讲解 Verilog 的基本概念。

– 以实例驱动学习,简化复杂理论,提升理解效率。

– 每个电路均附带完整的理论解释,帮助学员建立扎实的知识体系。

– 提供每个设计的测试平台(Testbench),并教授如何测试与验证电路功能。

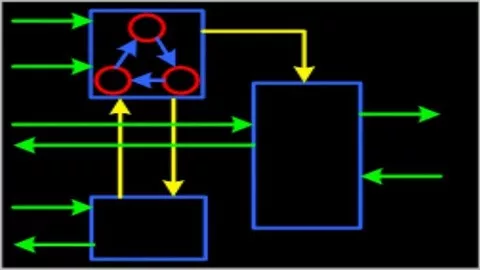

– 学习在 Verilog 中构建有限状态机(FSM)。

– 提供所有电路代码与设计资源,便于实践与复用。

– 指导使用 EDA Playground 工具进行 Verilog 编码,并通过 EPWave 生成输出波形。

– 详解 Verilog 关键概念:抽象层级、赋值类型、延迟生成、时钟创建、过程赋值等。

* **适用人群**:

– 有志于学习数字电子设计的工程师或学生。

* **课程目标**:

– 掌握 Verilog HDL 的语法与设计方法。

– 能够使用 Verilog 建模复杂数字系统(如加法器、多路复用器、状态机等)。

– 理解数字电路的时序分析与验证流程。

* **课程结构**:

– 通过 15 个章节、41 个视频讲座,系统讲解 Verilog 的基础到高级应用。

– 包含多个实际案例(如半加法器、全加法器、BCD 到 Gray 码转换器等),覆盖组合逻辑与时序逻辑设计。

– 提供理论讲解与代码实践相结合的学习路径,适合零基础入门及进阶学习。