Verilog HDL: VLSI 硬件设计综合大师班

来自拥有15年以上经验的专家,涵盖VLSI、SoC、处理器和FPGA的核心设计原则,VHDL的替代方案

学习内容:

* 无限的教练支持!

* 专用集成电路 (ASIC) 设计流程及其相关基础知识

* 学习足够多的知识,可以开始使用 HDL 设计实际电路

* 清楚了解如何编写和不编写 HDL 代码

* 硬件与代码的密切关系

* 从基础知识到设计工程师的关键原则

* 对每一部分代码和硬件的详细讨论

课程内容主题:

* Verilog Basics

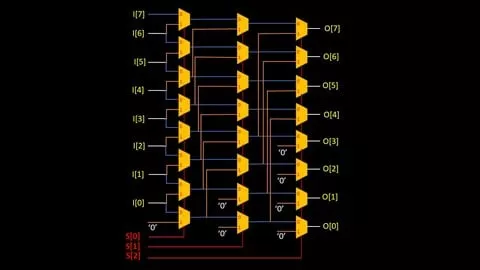

* Designing Combinational Logic

* Designing Sequential Logic

* Designing Memories

* Designing Finite State Machines

课程要求:

* 热爱学习,并定期系统地进行练习

* 数字逻辑设计基础

* 超大规模集成电路基础

* 任何编码经验都会有所帮助(非必需)

* 计算机体系结构

课程详细描述:

* 一门以工作为导向、使用 Verilog 硬件描述语言进行硬件逻辑设计的详尽课程。

* 遵循独特、经过测试和验证的结构化风格和方法。

* 将理论与实践巧妙结合,方便学习。

* 教练提供无限支持,帮助理解硬件设计的复杂细节。

* 通过多个实例强化设计原则,提供良好的编码指南及应避免的不良示例。

* 完成课程后,可自信编写可综合的复杂硬件设计代码。

* 详细讨论每个硬件组件设计,解析代码与数字硬件单元的关系。

* 提供课程中使用的100多个代码示例和测试平台的免费下载。

* 包含大量测验和作业,帮助检验学习成果。

* 学员可按自己的节奏学习课程内容。

适合人群:

* 初学者或中级水平,渴望掌握和理解 HDL 硬件设计概念

* 有志于在 VLSI 电路设计领域建立职业生涯的人

* 处于行业中的从业者,希望提升技能并深化理解

声明:本站所有文章,如无特殊说明或标注,均为本站发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。